偏离摩尔定律晶片微缩脚步渐缓 |

| 编辑:重庆亮键电子科技有限公司 字号:大 中 小 |

| 摘要:偏离摩尔定律晶片微缩脚步渐缓 |

半导体产业正在面临一项挑战,即每两年微缩晶片特征尺寸的周期已然结束,我们正在跨入一个情势高度不明的阶段。业界目前面临的几项关键挑战都显示,晶片微缩的路程愈来愈艰困了。 半导体产业正在面临一项挑战,即每两年微缩晶片特征尺寸的周期已然结束,我们正在跨入一个情势高度不明的阶段。业界目前面临的几项关键挑战都显示,晶片微缩的路程愈来愈艰困了。

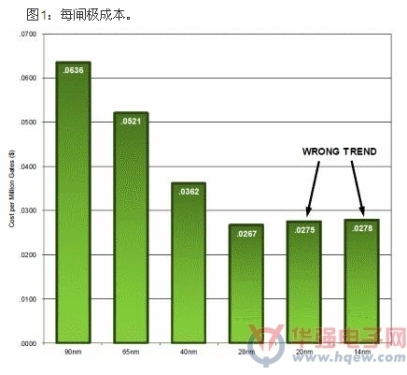

1。晶圆代工厂量产32/28nm晶圆的周期延长到了三年左右。2009年,45/40nm晶圆占代工厂营收比重仅10%;而2012年第四季,32/28nm占代工厂营收比重也是10%。 2。在32nm量产2年多以后,22nm的FinFET才宣布将迈入量产。FinFET是一项极具挑战性的技术。英特尔在这方面的研究相当卓越,但仍需克服许多挑战,才能支援新一代SoC所需的多阈值电压和多VDD位准。 3。与28nm制程相比,下一代20nm平面CMOS将面临更多的容差控制挑战。这可能带来重大影响──20nm的每闸极成本将高于28nm。 图:每闸极成本。 由于每闸极成本很可能会升高,因此,在迈向下一代制程时要做的工作实际上还有很多,这会再延长设计完成的时间。另外,14nm世代的每闸极成本也可能比28nm来得高。 4.20nm以后的下一步是什么?半导体产业正致力于开发14nmFinFET。他们确实能开发出来,但在制造上会面临更多挑战,包括阶梯覆盖(stepcoverage)、FIN尺寸的控制、在多个层上使用双重图形(doublepatterning),甚至需要使用四重图形等。 此外,EUV技术显然不会在2014~2015年就绪,所以业界仍得继续使用193nm工具。而最近检视28nm生产线的问题也显示,许多技术正在逼近极限。 另一个关键问题是FinFET能否实现晶片上的多VDD位准和多阈值电压。 业界要做的工作很多,必须开发新的元件库、IP必须过渡到FinFET架构、必须测试晶片的运作,还要确保能够量产。在14nm世代,复杂的晶片将花费2亿~5亿美元的设计成本,即使是返工也必须花费2,000万~5,000万美元。更不用提设计失败的成本了。 更重要的是,直到2016或2017年,看来都不会有英特尔以外的公司量产14nmFinFET。要达到量产阶段,就必须确保能达到比前几代技术更低的功耗,以及更更的每闸极成本。 而在14nm以后,还会面临全新的挑战(EUV、450mm、碳奈米管等)。半导体产业必须了解艰巨的挑战会不断迎面而来,而且朝更小特征尺寸转移的时间也会不断延长。 这代表整个供应链,包括模具供应商、光罩厂商、代工厂、IC设计公司和电子产品制造商都必须进行调整。 从硬体角度来看,苹果(Apple)这次推出新一代iPad时所做的最主要调整,只有更高解析度的显示器罢了。 对晶圆供应商来说,若他们不做出相应调整,那么每月10,000片晶圆,高达10亿美元的成本,是非常惊人的。 |

| 上一条:暂时没有! | 下一条:Molex子公司Temp-Flex推出新型微波同轴电缆 |